### **University of South Carolina** Scholar Commons

Theses and Dissertations

6-30-2016

# Modeling and Loss Analysis of Wide Bandgap Power Semiconductor Devices

Kang Peng University of South Carolina

Follow this and additional works at: http://scholarcommons.sc.edu/etd

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Peng, K.(2016). Modeling and Loss Analysis of Wide Bandgap Power Semiconductor Devices. (Doctoral dissertation). Retrieved from http://scholarcommons.sc.edu/etd/3384

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

## MODELING AND LOSS ANALYSIS OF WIDE BANDGAP POWER SEMICONDUCTOR DEVICES

by

Kang Peng

Bachelor of Science Hunan University, 2008

Master of Science Huazhong University of Science and Technology, 2011

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

**Electrical Engineering**

College of Engineering and Computing

University of South Carolina

2016

Accepted by:

Enrico Santi, Major Professor

Grigory Simin, Committee Member

Krishna Mandal, Committee Member

Chen Li, Committee Member

Lacy Ford, Senior Vice Provost and Dean of Graduate Studies

© Copyright by Kang Peng, 2016 All Rights Reserved.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my Ph.D advisor, Dr. Enrico Santi, for his guidance and support in my doctoral study at University of South Carolina, Columbia. With his great knowledge, patience and wisdom, Dr. Santi always shows a bright way to me about my research and study. His support and encouragement has made my Ph.D study an enjoyable journey. Also I would like to thank my committee members: Dr. Grigory Simin, Dr. Krishna Mandal and Dr. Chen. Li for their valuable guidance in my research. Without their valuable help and feedback, the completion of this dissertation would be impossible.

I would also like to thank all my colleagues in power electronics group at USC I worked with. I cherish the wonderful time that we worked together. I would like to express my sincere gratitude to Dr. Alexander Grekov, Dr. Daniel Martin, Dr. Ruiyun Fu, Dr. Isaac Nam, Dr. Antonino Riccobono, Ozan Gulbudak, and Jonathan Siegers.

Finally, I would like to express my greatest appreciation for years of love and support to my dear parents, Jianping Peng and Xinglan Liu.

#### **ABSTRACT**

In recent times, the development of high power density and high efficiency power converters has become critical in power electronics applications like electric vehicles, aircrafts, electric ships and so on. High-switching-frequency and high-temperature operation are required to achieve this target. However, these requirements are exceeding the theoretical material-related limits of silicon (Si) based devices. The emerging wide bandgap power semiconductor technology is a promising solution to meet these requirements. Silicon Carbide (SiC) and Gallium Nitride (GaN) are the most promising among all wide bandgap semiconductor materials. SiC and GaN have almost a three times larger bandgap (about 3eV), compared with Si (about 1eV). The breakdown electric field of SiC and GaN is one order of magnitude higher than that of Si. The higher breakdown electric field enables the design of wide bandgap power devices with a thinner and higher doped voltage blocking layer. For unipolar power devices, this can yield a lower on-state voltage drop and conduction loss. For bipolar power devices, this can lead to a shorter switching time and lower switching loss. The high thermal conductivity of SiC, together with large bandgap, allows SiC-based devices to operate at temperatures exceeding 200°C. All of these properties make wide bandgap semiconductor devices a promising alternative to Si-based devices.

The research work in this Ph.D dissertation can be broadly divided into two parts: the development of power device models, and the development of loss models for wide

bandgap power devices.

First, in order to characterize the switching performance of GaN High Electron Mobility Transistor (HEMT), a simple and accurate circuit-simulator compact model for a normally-off GaN HEMT device is developed. The model parameters can be easily extracted from static I-V characteristics and C-V characteristics. This model captures reverse channel conduction, which is a very important feature for circuit designers. A parameter extraction method is proposed. A double pulse test-bench is built to test the switching behavior of GaN HEMT. The accuracy of the proposed GaN HEMT model is validated under resistive and inductive switching conditions, and simulation results match well with experiments in terms of device switching waveforms.

Second, the static and switching characterizations of a SiC MOSFET's body diode are carried out. The static characterization of SiC MOSFET's body diode is done using a curve tracer and a double pulse test bench is built to characterize the inductive switching behavior of SiC MOSFET's body diode. The reverse recovery of SiC MOSFET's body diode is shown at different junction temperatures, forward conduction currents and current commutation slopes. In order to evaluate the performance of SiC MOSFET's body diode in different applications, an accurate physics-based diode model is introduced to perform simulations of SiC MOSFET's body diode. The validation of the body diode model is presented to prove the accuracy of the device model over a wide temperature range.

Third, an accurate analytical loss model that takes into account parasitic elements for power converters utilizing SiC MOSFETs and SiC Schottky diodes is proposed. A novel feature of this loss model is that it considers the PCB parasitic elements in the

circuits and the ringing loss. The switching process is analyzed in details, and the typical switching waveforms are given. The analytical results are compared with experimental results to verify the proposed analytical loss model.

Finally, a performance projection method and scalable loss model for SiC MOSFETs and SiC Schottky diodes are developed. To our knowledge, this is the first scalable loss model that provides performance projection capability for future SiC MOSFETs and SiC Schottky diodes. The parameters of these models are extracted from device datasheets by using a curve fitting method. Loss estimation of future SiC MOSFETs and SiC Schottky diodes can be performed based on the proposed scalable loss model.

### TABLE OF CONTENTS

| ACKNO   | WLEDGEMENTS                                              | ii    |

|---------|----------------------------------------------------------|-------|

| ABSTRA  | ACT                                                      | iv    |

| LIST OI | F TABLES                                                 | Х     |

| LIST OF | F FIGURES                                                | X     |

| LIST OF | F SYMBOLS                                                | .xvii |

| CHAPTI  | ER 1 INTRODUCTION                                        | 1     |

| 1.1     | WIDE BANDGAP SEMICONDUCTOR DEVICES FOR POWER ELECTRONICS | 1     |

| 1.2     | RESEARCH MOTIVATIONS AND OBJECTIVES                      | 6     |

| 1.3     | STATE OF THE ART IN RESEARCH                             | 9     |

| 1.4     | Contributions                                            | 13    |

| 1.5     | DISSERTATION ORGANIZATION                                | 15    |

|         | ER 2 CHARACTERIZATION AND MODELING OF A GALLIUM NITRI    |       |

| 2.1     | DEVELOPMENT OF DEVICE SIMULATION MODEL                   | 18    |

| 2.2     | STATIC CHARACTERIZATION AND PARAMETER EXTRACTION         | 24    |

| 2.3     | MODEL VALIDATION                                         | 33    |

| 2.4     | Summary                                                  | 47    |

|     | ER 3 CHARACTERIZATION AND MODELING OF SIC MOSFET BO<br>DIODE                         |     |

|-----|--------------------------------------------------------------------------------------|-----|

| 3.1 | STATIC CHARACTERISTICS                                                               | 51  |

| 3.2 | Double Pulse Tester                                                                  | 55  |

| 3.3 | SWITCHING CHARACTERISTICS                                                            | 57  |

| 3.4 | BODY DIODE MODEL DEVELOPMENT                                                         | 65  |

| 3.5 | PARAMETER EXTRACTION                                                                 | 74  |

| 3.6 | MODEL VALIDATION                                                                     | 78  |

| 3.7 | Summary                                                                              | 81  |

|     | ER 4 ANALYTICAL LOSS MODEL FOR POWER CONVERTERS W MOSFET AND SIC SCHOTTKY DIODE PAIR |     |

| 4.1 | PROPOSED ANALYTICAL LOSS MODEL                                                       | 84  |

| 4.2 | EXPERIMENTAL VERIFICATION OF THE ANALYTICAL LOSS MODEL                               | 104 |

| 4.3 | DISCUSSION                                                                           | 114 |

| 4.4 | Summary                                                                              | 116 |

|     | ER 5 PERFORMANCE PROJECTION AND SCALABLE LOSS MODES                                  |     |

| 5.1 | Introduction                                                                         | 118 |

| 5.2 | PERFORMANCE PROJECTION METHOD                                                        | 120 |

| 5.3 | SCALABLE LOSS MODEL                                                                  | 125 |

| 5.4 | LOSS ANALYSIS OF A SIC BOOST CONVERTED                                               | 131 |

| 5.5    | SUMMARY                          | 135 |

|--------|----------------------------------|-----|

| СНАРТІ | ER 6 CONCLUSIONS AND FUTURE WORK | 136 |

| 6.1    | Conclusions                      | 136 |

| 6.2    | FUTURE WORK                      | 138 |

| REFERE | ENCES                            | 140 |

### LIST OF TABLES

| Table 1.1 | Physical characteristics of Si, SiC and GaN                                                                               | 2   |

|-----------|---------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.1 | GaN HEMT model parameters                                                                                                 | 23  |

| Table 2.2 | Extracted model parameter values for EPC 2001                                                                             | 33  |

| Table 2.3 | Resistive switching results                                                                                               | 41  |

| Table 3.1 | Body diode model parameter list                                                                                           | 74  |

| Table 3.2 | Extracted model parameter values for SiC MOSFET body diode                                                                | 79  |

| Table 5.1 | Current status of mature SiC MOSFETs from Cree                                                                            | 120 |

|           | Specific on resistance of the SiC DMOSFETs measured at gate bias of 20V function of breakdown voltage at room temperature |     |

| Table 5.3 | Nominal energy loss from device datasheet                                                                                 | 127 |

| Table 5.4 | Specifications of a SiC DC-DC boost converter                                                                             | 132 |

### LIST OF FIGURES

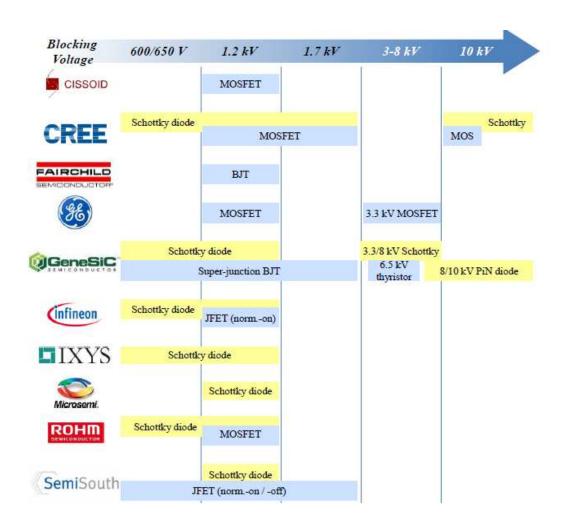

| Figure 1.1 Major SiC power device manufacturers and their relevant products [8]                            | 3    |

|------------------------------------------------------------------------------------------------------------|------|

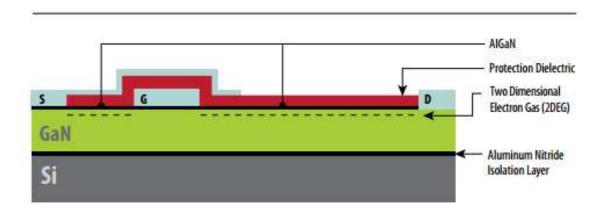

| Figure 1.2 GaN HEMT structure [10]                                                                         | 5    |

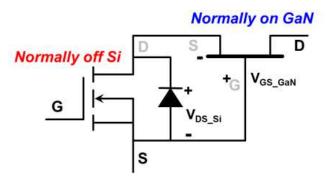

| Figure 1.3 Cascode structure for depletion-mode GaN HEMT                                                   | 6    |

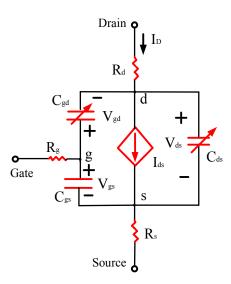

| Figure 2.1 Structure of the GaN HEMT model                                                                 | . 19 |

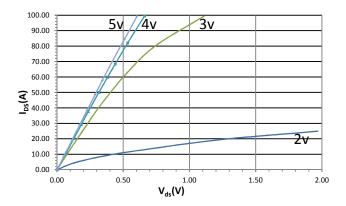

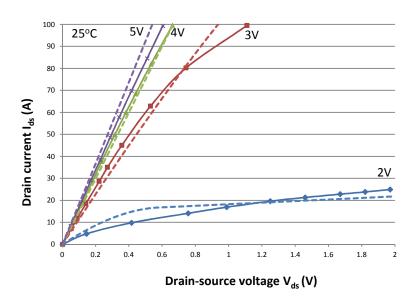

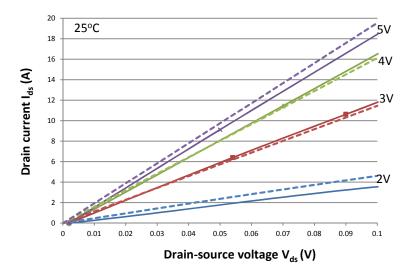

| Figure 2.2 Measured forward output I-V characteristics at room temperature 25°C for EPC2001                | . 25 |

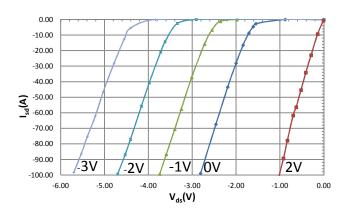

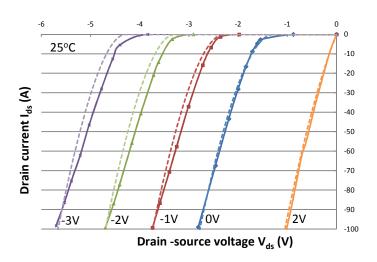

| Figure 2.3 Measured reverse output I-V characteristics at room temperature 25°C for EPC2001                | . 25 |

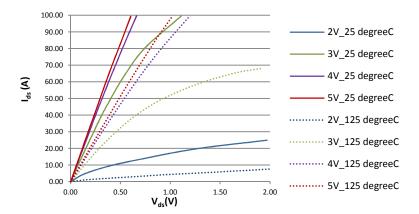

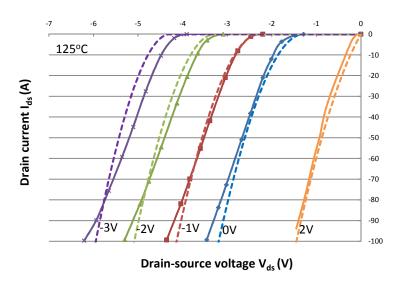

| Figure 2.4 Measurement of forward output I-V characteristics at 25°C (solid) and 125° (dashed)             |      |

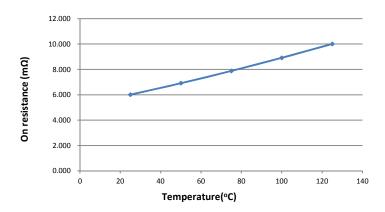

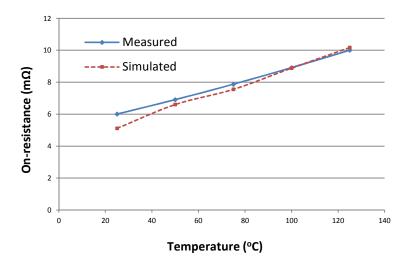

| Figure 2.5 Measured on resistance of GaN HEMT at 5V gate-source voltage as a funct of junction temperature |      |

| Figure 2.6 Measurement of reverse output I-V characteristics at 25°C (solid) and 125 °C (dashed)           |      |

| Figure 2.7 Measurement of transfer characteristics at room temperature 25°C                                | . 27 |

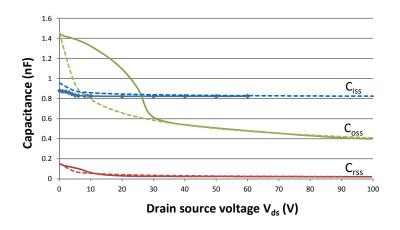

| Figure 2.8 Measured capacitances versus drain-to-source voltage for EPC 2001                               | . 28 |

| Figure 2.9 The plot of the square root of $I_{ds}$ vs. gate-source voltage                                 | . 29 |

| Figure 2.10 The plot of the square root of I <sub>sd</sub> vs. gate-drain voltage                          | . 30 |

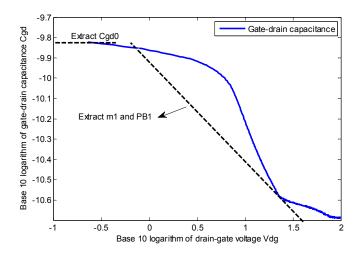

| Figure 2.11 The log-log plot of C <sub>gd</sub> vs. drain-gate voltage                                     | . 30 |

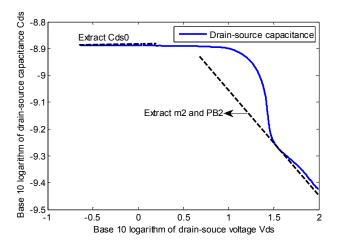

| Figure 2.12 The log-log plot of C <sub>ds</sub> vs. drain-source voltage                                   | . 31 |

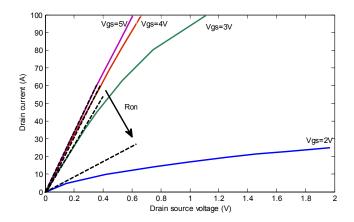

| Figure 2.13 Forward conduction output characteristics and on-resistance extraction                         | . 32 |

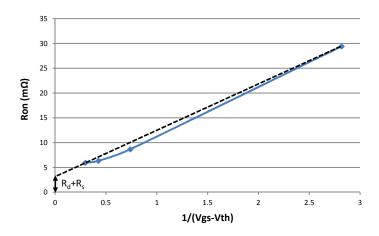

| Figure 2.14 The plot of on-resistance R <sub>on</sub> vs. 1/(V <sub>gs</sub> -V <sub>th1</sub> )           | . 32 |

| Figure | 2.15 Forward I-V characteristics comparison between simulation (dashed) and measurement (solid) at room temperature 25°C                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2.16 Forward I-V characteristics comparison between simulation (dashed) and measurement (solid) in linear region (zoom-in of prior figure) at room temperature 25°C |

| Figure | 2.17 Reverse I-V characteristics comparison between simulation (dashed) and measurement (solid) at room temperature 25°C                                            |

| Figure | 2.18 Forward I-V characteristics comparison between simulation (dashed) and measurement (solid) at 125°C                                                            |

| Figure | 2.19 Reverse I-V characteristics comparison between simulation (dashed) and measurement (solid) at 125°C                                                            |

| Figure | 2.20 On-resistance comparison between simulation (dashed) and measurement (solid) at 5V gate-source voltage                                                         |

| Figure | 2.21 Comparison of C-V characteristics between simulation (dashed) and measurement (solid)                                                                          |

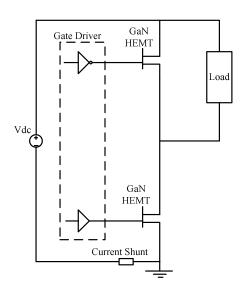

| Figure | 2.22 Double pulse test schematic                                                                                                                                    |

| Figure | 2.23 Picture of double pulse tester PCB board                                                                                                                       |

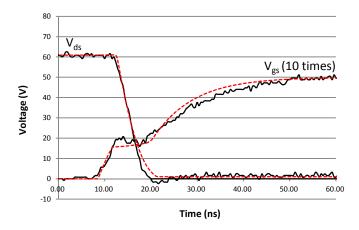

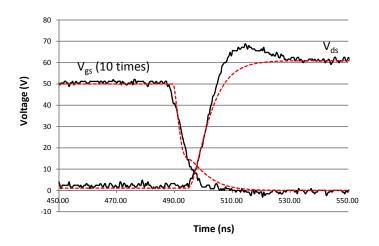

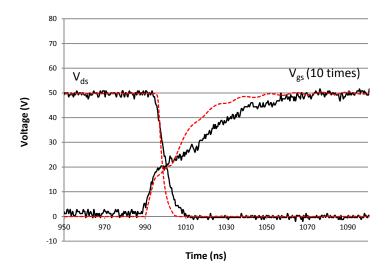

| Figure | 2.24 Simulated (dashed) and experimental (solid) turn-on voltage waveforms of resistive switching                                                                   |

| Figure | 2.25 Simulated (dashed) and experimental (solid) turn-off voltage waveforms of resistive switching                                                                  |

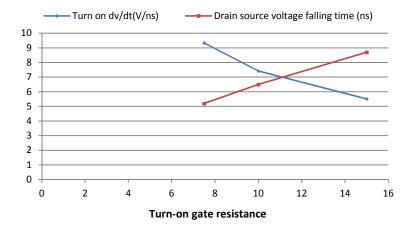

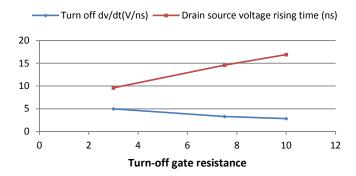

| Figure | 2.26 Turn-on dV/dt and drain source voltage falling time dependence on turn-on gate resistance                                                                      |

| Figure | 2.27 Turn-off dV/dt and drain source voltage rising time dependence on turn-off gate resistance                                                                     |

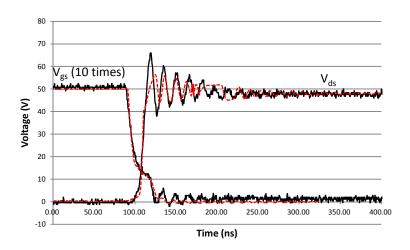

| Figure | 2.28 Simulated (dashed) and experimental (solid) turn-on voltage waveforms of inductive switching                                                                   |

| Figure | 2.29 Simulated (dashed) and experimental (solid) turn-off voltage waveforms of inductive switching                                                                  |

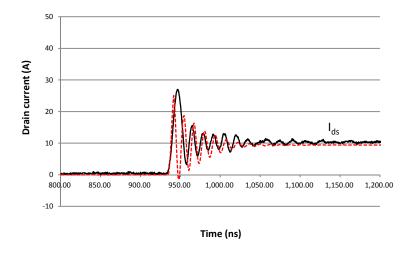

| Figure | 2.30 Simulated (dashed) and experimental (solid) turn-on current waveforms of inductive switching                                                                   |

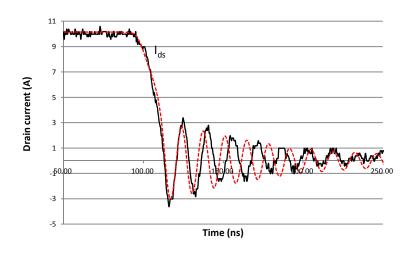

| Figure | 2.31 Simulated (dashed) and experimental (solid) turn-off current waveforms of inductive switching                                                                      |    |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

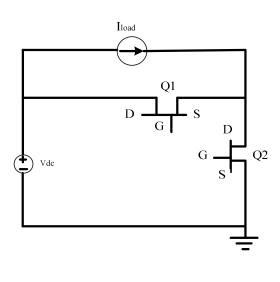

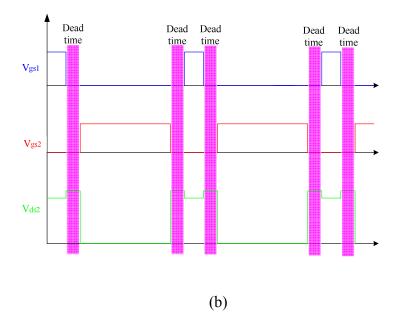

| Figure | 2.32 (a) Double pulse test schematic (b) Gate drive signals showing the dead tin introduced to prevent cross-conduction                                                 |    |

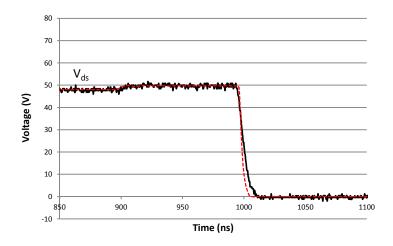

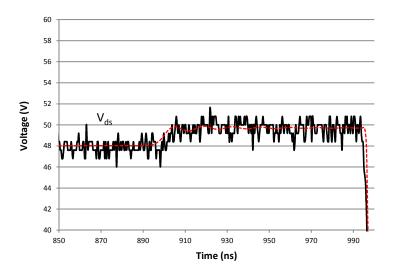

| Figure | 2.33 Comparison of simulated (dashed) and experimental (solid) drain-source voltage waveforms of Q2 at turn-on transition                                               | 46 |

| Figure | 2.34 Comparison of simulated (dashed) and experimental (solid) drain-source voltage waveforms of Q2 at turn-on transition (zoom-in of prior figure)                     | 47 |

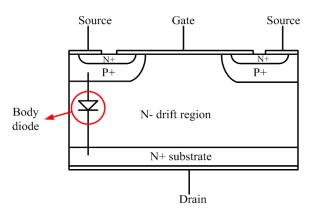

| Figure | 3.1 Cross-sectional structure schematic of power SiC DMOSFET                                                                                                            | 50 |

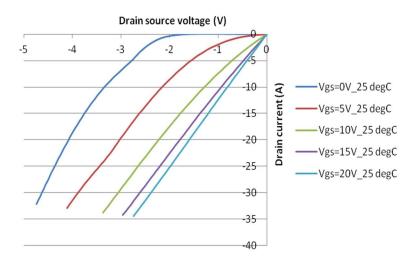

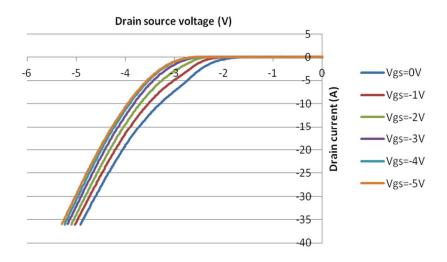

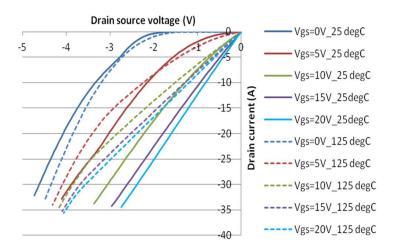

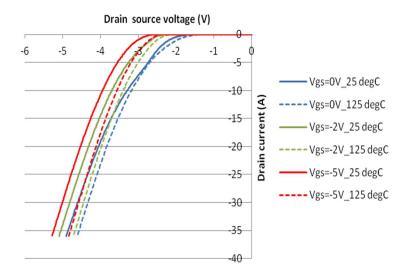

| Figure | 3.2 Static characteristics of SiC MOSFET body diode with positive gate-source voltages                                                                                  | 51 |

| Figure | 3.3 Static characteristics of SiC MOSFET body diode with negative gate-source voltages                                                                                  |    |

| Figure | 3.4 Static characteristics of SiC MOSFET body diode with positive gate-source voltages at 25°C and 125°C                                                                | 53 |

| Figure | 3.5 Static characteristics of SiC MOSFET body diode with negative gate-source voltages at 25°C and 125°C                                                                |    |

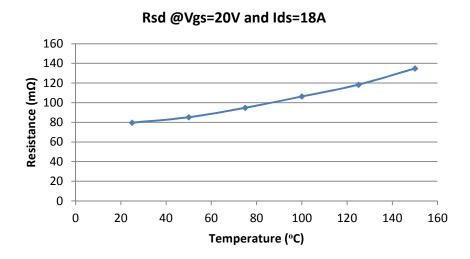

| Figure | 3.6 On-state resistance of SiC MOSFET as a function of temperature                                                                                                      | 54 |

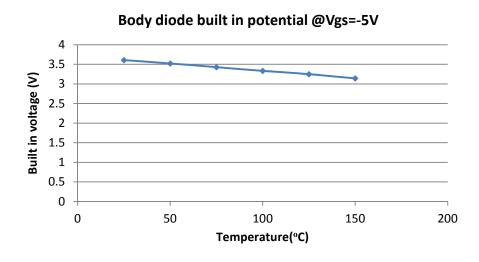

| Figure | 3.7 Body diode built-in potential of SiC MOSFET body diode as a function of temperature                                                                                 | 54 |

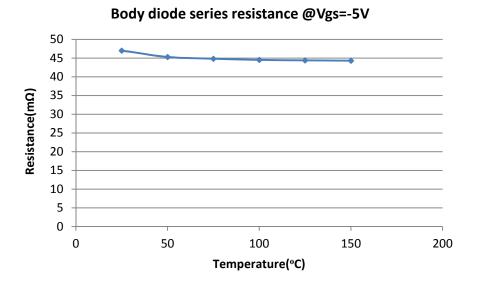

|        | 3.8 Body diode series resistance of SiC MOSFET body diode as a function of temperature                                                                                  | 55 |

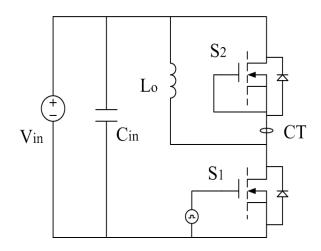

| Figure | 3.9 Schematic of double pulse tester                                                                                                                                    | 56 |

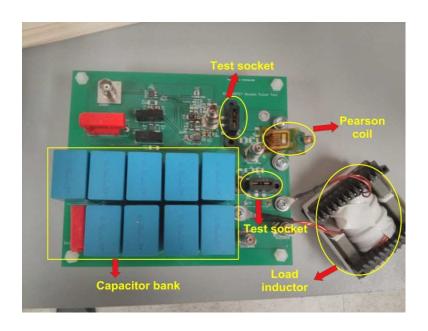

| Figure | 3.10 Picture of double pulse tester                                                                                                                                     | 56 |

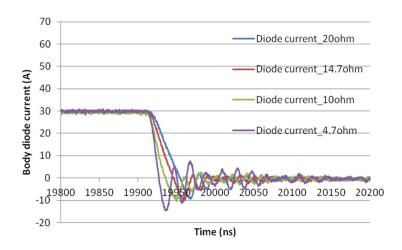

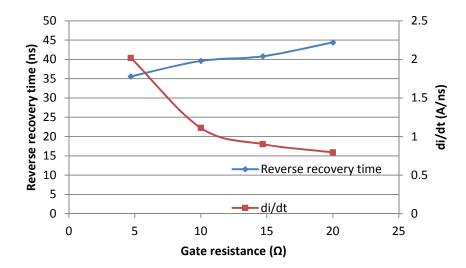

| Figure | 3.11 Body diode current waveforms at different low-side SiC MOSFET gate resistances (block voltage: 500V, forward conduction current: 30A)                              | 57 |

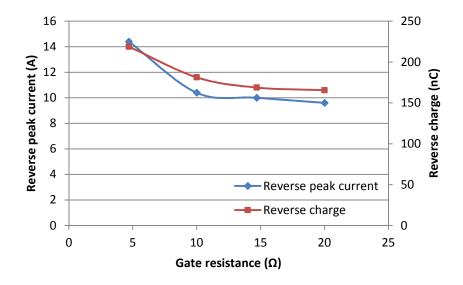

| Figure | 3.12 Body diode reverse peak currents and reverse recovery charges at different low-side MOSFET gate resistances (block voltage: 500V, forward conduction current: 30A) | 50 |

| Figure | 3.13 Body diode reverse recovery times and di/dt at different low-side MOSFET gate resistances (block voltage: 500V, forward conduction current: 30A)                                                                                |    |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

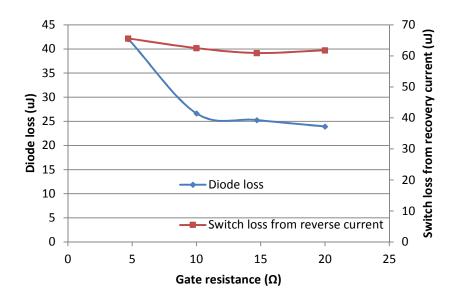

| Figure | 3.14 Body diode reverse recovery switching losses and switching losses from reverse current in complementary switch at different low-side MOSFET gate resistances (block voltage: 500V, forward conduction current: 30A)             | 59 |

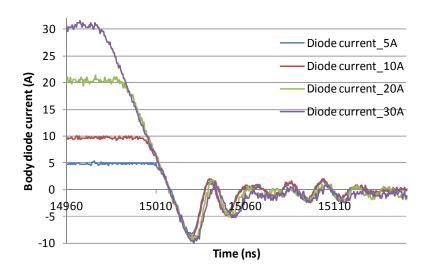

| Figure | 3.15 Body diode current waveforms at different forward conduction currents (block voltage: $500V$ , gate resistance: $20\Omega$ )                                                                                                    | 50 |

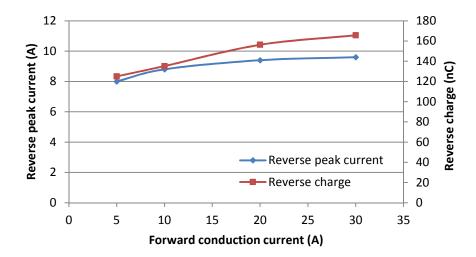

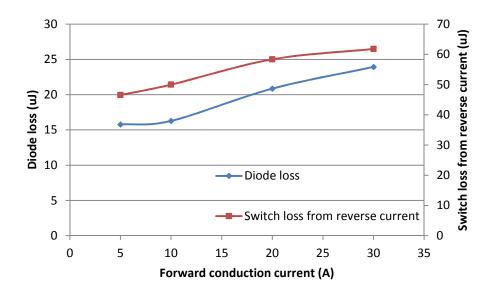

| Figure | 3.16 Body diode reverse peak currents and reverse charges at different forward conduction currents (block voltage: $500V$ , gate resistance: $20\Omega$ )                                                                            | 51 |

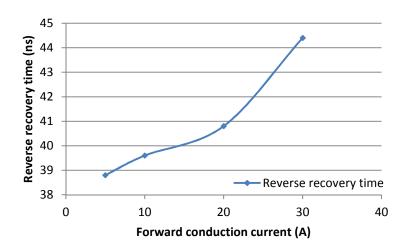

| Figure | 3.17 Body diode reverse recovery times at different forward conduction currents (block voltage: $500V$ , gate resistance: $20\Omega$ )                                                                                               |    |

| Figure | 3.18 Body diode reverse recovery switching losses and switching losses from reverse current in complementary switch at different forward conduction current (block voltage: $500V$ , gate resistance: $20\Omega$ )                   |    |

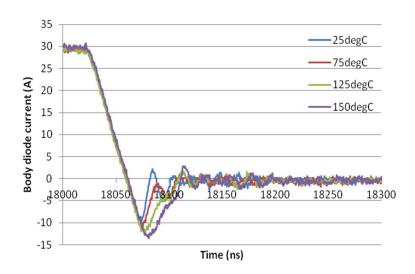

| Figure | 3.19 Body diode current waveforms at different temperatures (block voltage: 500V, gate resistance: $20\Omega$ , forward conduction current: $30A$ )                                                                                  | 53 |

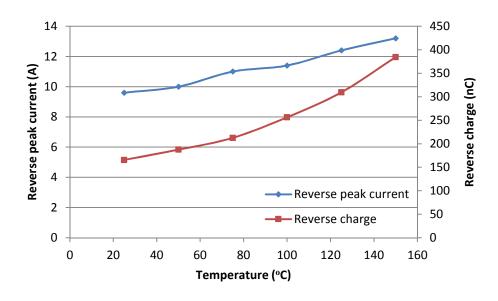

| Figure | 3.20 Body diode reverse peak current and reverse charge at different temperature (block voltage: $500V$ , gate resistance: $20\Omega$ , forward conduction current: $30A$ )                                                          |    |

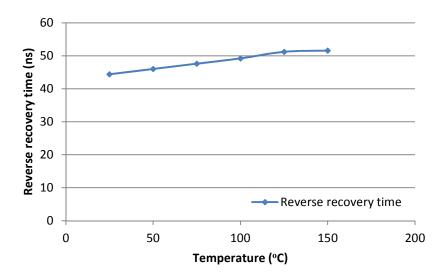

| Figure | 3.21 Body diode reverse recovery times at different temperatures (block voltage: 500V, gate resistance: $20\Omega$ , forward conduction current: $30A$ )                                                                             |    |

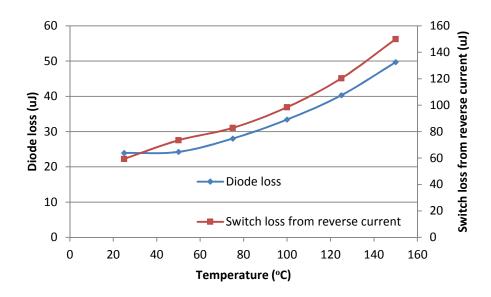

| Figure | 3.22 Body diode reverse recovery switching losses and switching losses from reverse current in complementary switch at different temperatures (block voltage 500V, gate resistance: $20\Omega$ , forward conduction current: $30A$ ) |    |

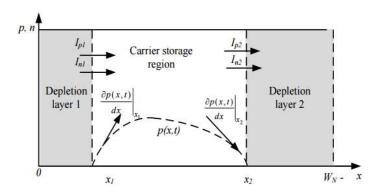

| Figure | 3.23 Carrier storage layer and depletions layers in n-drift region                                                                                                                                                                   | 55 |

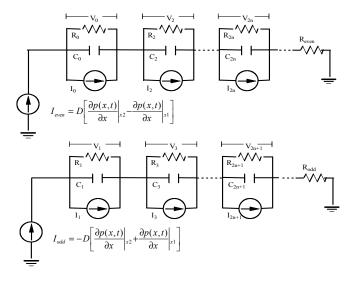

| Figure | 3.24 Equivalent circuit used to calculate the carrier density representing the coefficients of the Fourier series solution to ADE                                                                                                    | 57 |

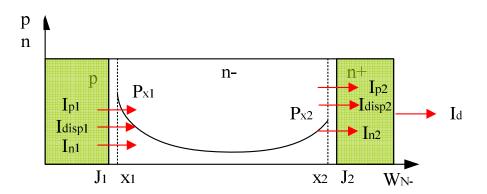

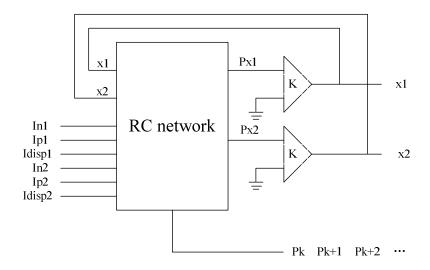

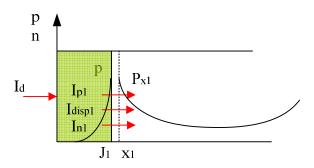

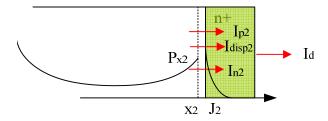

| Figure | 3.25 Schematic structure and carrier densities of drift region of a SiC MOSFET body diode during on-state                                                                                                                            | 58 |

| Figure | 3.26 Discretized carrier profile for simulation of V <sub>n</sub>                                                                                                                                                                    | 70 |

| Figure | 3.27 Feedback scheme for the calculation of $x_1$ and $x_2$                                                                                                                                                                          | 71 |

| Figure 3.28 Carrier distribution and currents in p end region of the body diode during the on-state                                    |

|----------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.29 Carrier distribution and currents in n+ end region of the body diode during the on-state                                   |

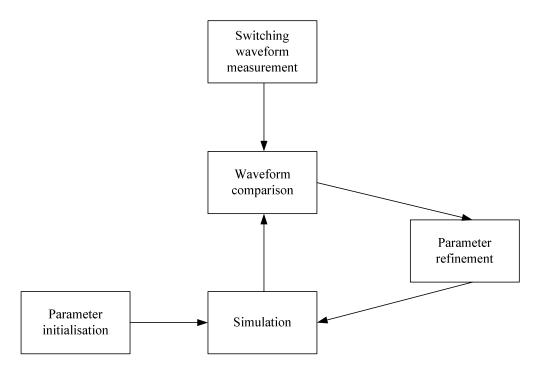

| Figure 3.30 The procedure of parameter extraction                                                                                      |

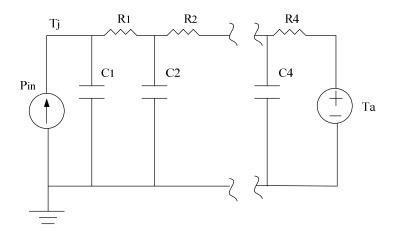

| Figure 3.31 Equivalent circuit used for thermal modeling                                                                               |

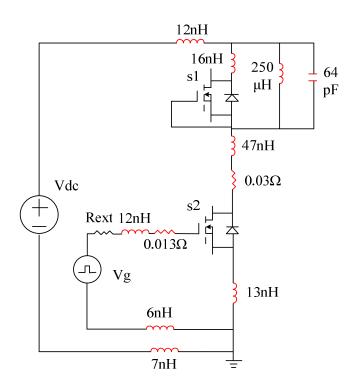

| Figure 3.32 Equivalent circuit used for inductive switching                                                                            |

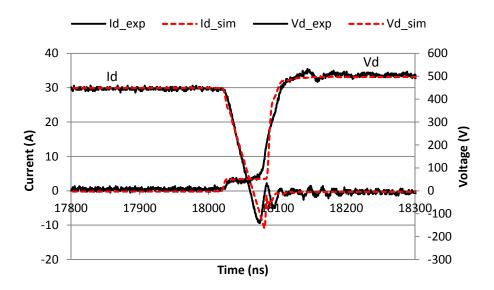

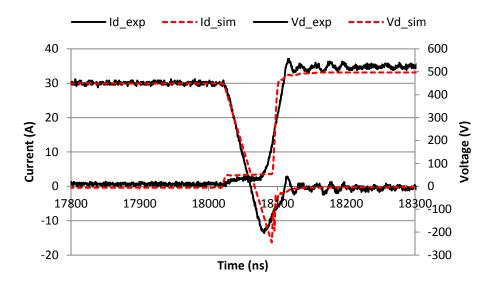

| Figure 3.33 The comparison of diode turn-off voltage and current waveforms between experiment (solid) and simulation (dashed) at 25°C  |

| Figure 3.34 The comparison of diode turn-off voltage and current waveforms between experiment (solid) and simulation (dashed) at 150°C |

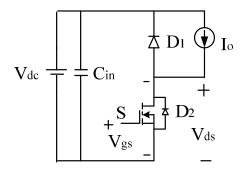

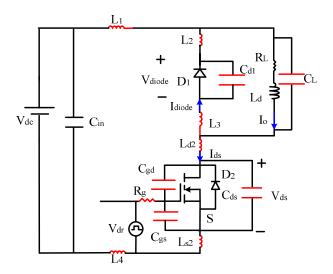

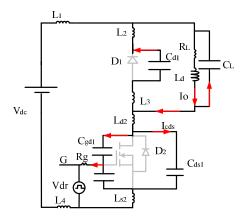

| Figure 4.1 Test circuit schematic                                                                                                      |

| Figure 4.2 Circuit with parasitic inductances and capacitances                                                                         |

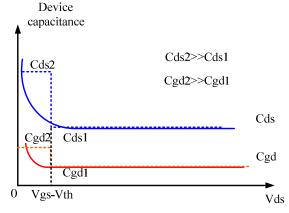

| Figure 4.3 Nonlinear capacitances $C_{gd}$ and $C_{ds}$ as a function of drain source voltage $V_{ds}$                                 |

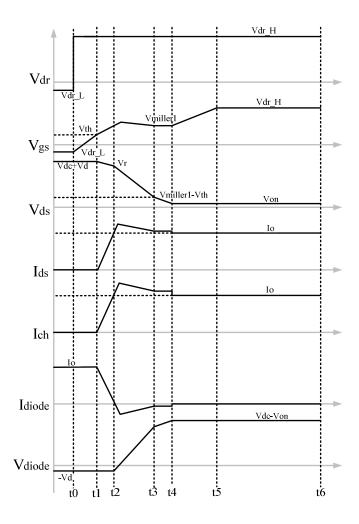

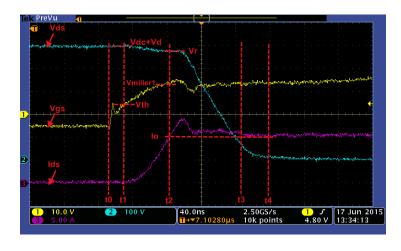

| Figure 4.4 Key waveforms of turn-on switching transition                                                                               |

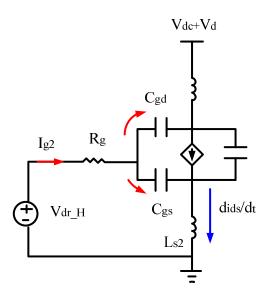

| Figure 4.5 MOSFET gate driving equivalent circuit during interval 2 [t <sub>1</sub> , t <sub>2</sub> ] 89                              |

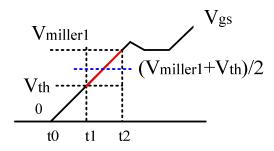

| Figure 4.6 Gate-source signal during interval 2 [t <sub>1</sub> , t <sub>2</sub> ]                                                     |

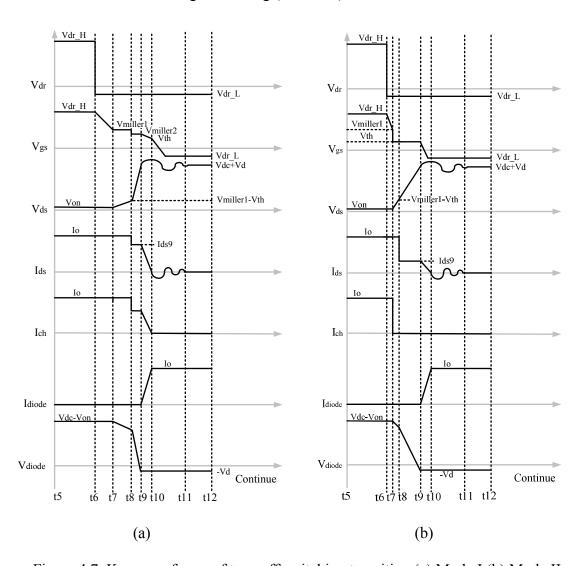

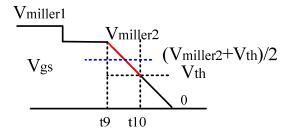

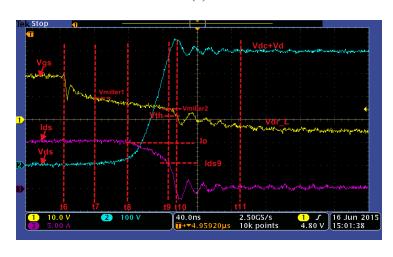

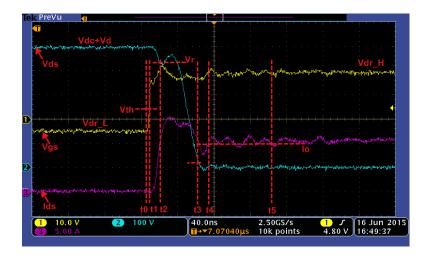

| Figure 4.7 Key waveforms of turn-off switching transition (a) Mode I (b) Mode II 94                                                    |

| Figure 4.8 MOSFET operation during interval 8 [t <sub>7</sub> , t <sub>8</sub> ]                                                       |

| Figure 4.9 Current conduction path during time period [t <sub>8</sub> , t <sub>9</sub> ] (Mode II)                                     |

| Figure 4.10 MOSFET gate driving equivalent circuit during time period [t <sub>9</sub> , t <sub>10</sub> ] 101                          |

| Figure 4.11 Gate signal during time period [t <sub>9</sub> , t <sub>10</sub> ]                                                         |

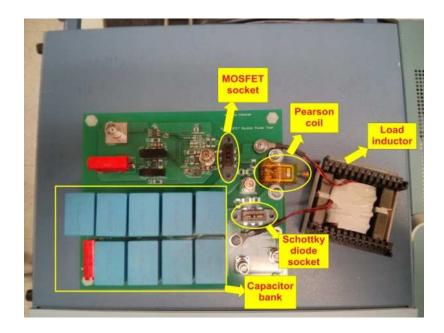

| Figure 4.12 Experimental setup of inductive switching tests                                                                            |

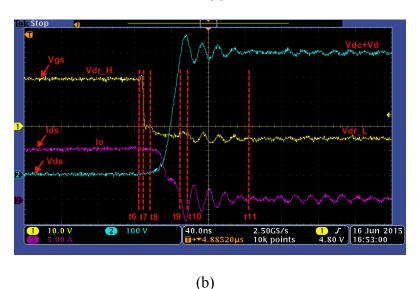

| Figure 4.13 SiC MOSFET switching waveforms (10A load current, $47\Omega$ gate                                                          |

| Figure 4.14 SiC MOSFET switching waveforms (10A load current, $3.3\Omega$ gate resistance)                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

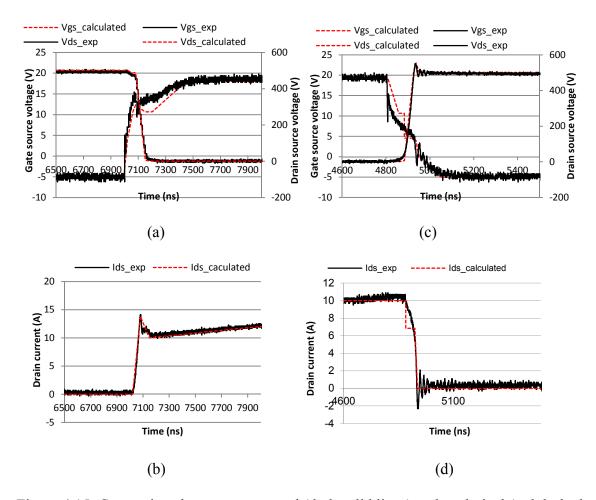

| Figure 4.15 Comparison between measured (dark solid lines) and analytical (red dashed lines) waveforms for (a) $V_{gs}$ and $V_{ds}$ at turn-on transition (b) $I_{ds}$ at turn-on transition (c) $V_{gs}$ and $V_{ds}$ at turn-off transition (d) $I_{ds}$ at turn-off transition (10A load current, 47 $\Omega$ gate resistance) |

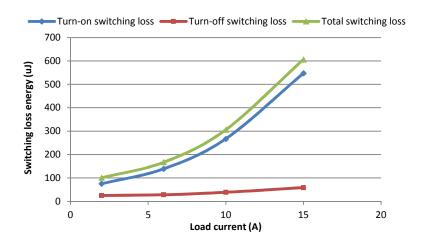

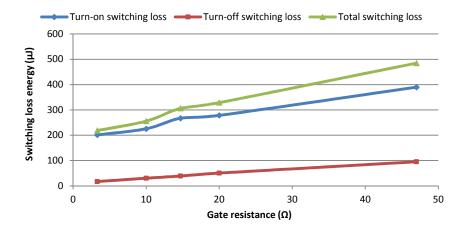

| Figure 4.16 Switching energy losses as a function of load current (experimental) 110                                                                                                                                                                                                                                               |

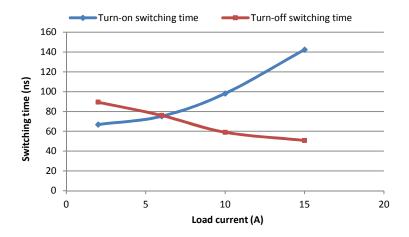

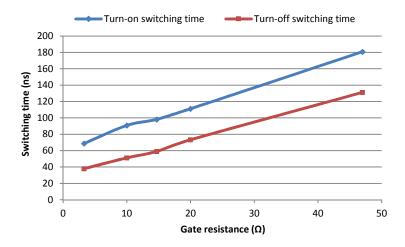

| Figure 4.17 Switching times as a function of load current (experimental)                                                                                                                                                                                                                                                           |

| Figure 4.18 Switching energy losses as a function of gate resistance (experimental) 111                                                                                                                                                                                                                                            |

| Figure 4.19 Switching times as a function of gate resistance (experimental)                                                                                                                                                                                                                                                        |

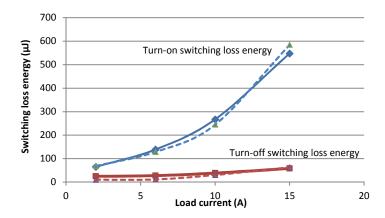

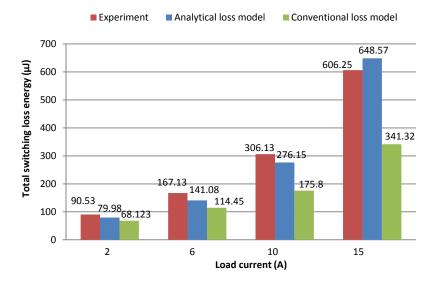

| Figure 4.20 Comparison of SiC MOSFET switching losses as a function of load current                                                                                                                                                                                                                                                |

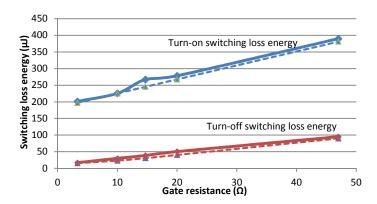

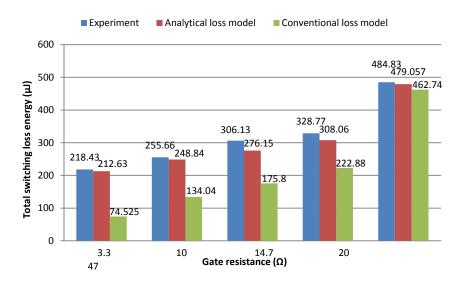

| Figure 4.21 Comparison of SiC MOSFET switching losses as a function of gate resistance                                                                                                                                                                                                                                             |

| Figure 4.22 Comparison of SiC MOSFET switching losses as a function of gate resistance                                                                                                                                                                                                                                             |

| Figure 4.23 Comparison of SiC MOSFET switching losses as a function of load current                                                                                                                                                                                                                                                |

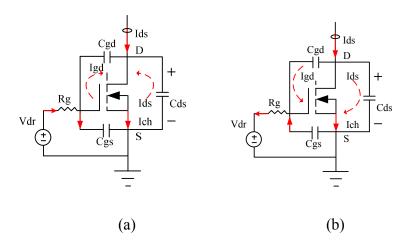

| Figure 4.24 SiC MOSFET operation (a) when drain-source voltage drops (b) when drain-source voltage rises                                                                                                                                                                                                                           |

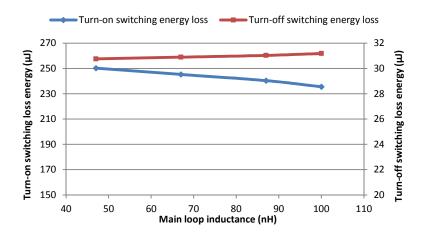

| Figure 4.25 Turn-on and turn-off switching energy losses under the influence of main loop parasitic inductance                                                                                                                                                                                                                     |

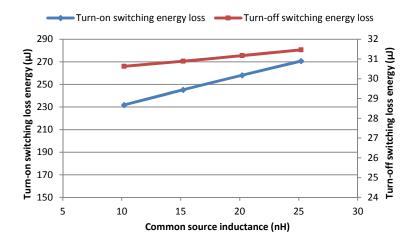

| Figure 4.26 Turn-on and turn-off switching energy losses under the influence of common source parasitic inductance                                                                                                                                                                                                                 |

| Figure 5.1 Ratings of SiC power MOSFETs available from Cree                                                                                                                                                                                                                                                                        |

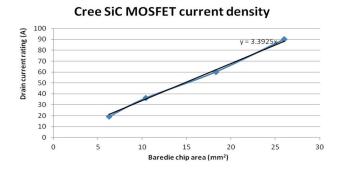

| Figure 5.2 SiC power MOSFET drain current rating (I <sub>D</sub> ) versus chip area (A <sub>chip</sub> ) 121                                                                                                                                                                                                                       |

| Figure 5.3 SiC power MOSFET thermal resistance (R <sub>th (J-C)</sub> ) versus chip area (A <sub>chip</sub> ) 122                                                                                                                                                                                                                  |

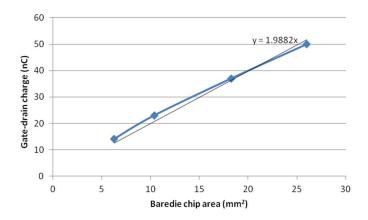

| Figure 5.4 SiC power MOSFET gate-drain charge (Q <sub>gd</sub> ) versus chip area (A <sub>chip</sub> ) 123                                                                                                                                                                                                                         |

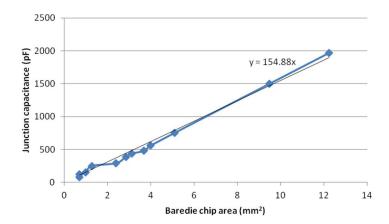

| Figure 5.5 SiC power MOSFET junction capacitance (C <sub>10</sub> ) versus chip area (A <sub>chip</sub> ) 125                                                                                                                                                                                                                      |

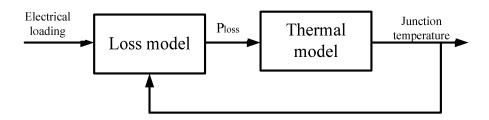

| Figure 5.6 Electro-thermal model                                                                                                               | 126 |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

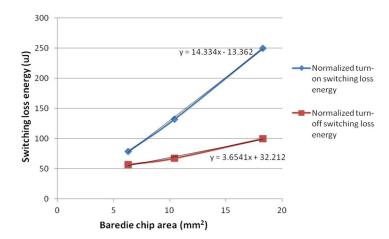

| Figure 5.7 SiC MOSFET nominal turn-on loss energy and nominal turn-off loss of V.S. chip area (A <sub>chip</sub> )                             |     |

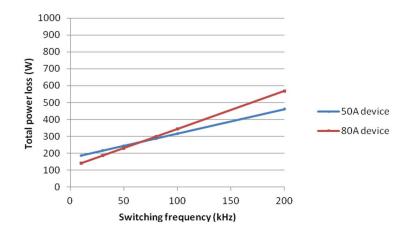

| Figure 5.8 Total power loss of SiC boost converter at full power as a function of switching frequency for two different device current ratings | 132 |

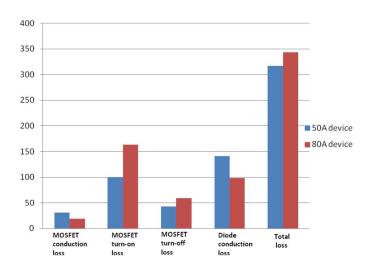

| Figure 5.9 Power loss breakdown of SiC boost converter at full power rating and switching frequency 100kHz                                     |     |

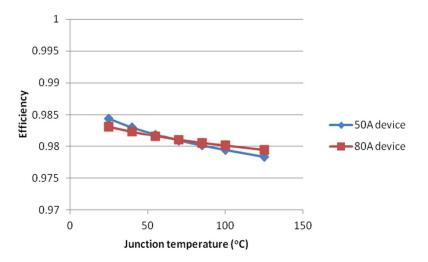

| Figure 5.10 Efficiency of SiC boost converter at full power (20 kW), switching frequency 100 kHz as a function of junction temperature         | 134 |

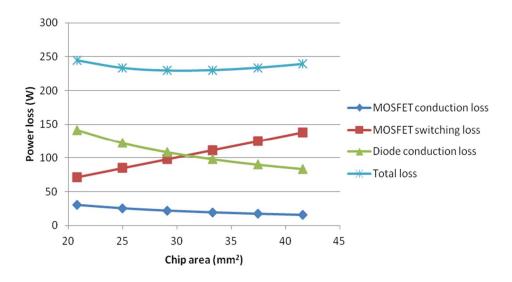

| Figure 5.11 Power loss distribution of SiC boost converter at full power rating 20 switching frequency 50 kHz with different chip areas        | ,   |

#### LIST OF SYMBOLS

$V_{sat}$  Carrier saturation velocity in silicon carbide (cm/s)

$\varepsilon_{SiC}$  Dielectric constant of silicon carbide (F/cm)

$\mu_n$  Electron mobility (cm<sup>2</sup>/V·s)

$\mu_p$  Hole mobility (cm<sup>2</sup>/V·s)

A Active area  $(cm^2)$

$C_{gd}$  Capacitance between gate and drain (F)

$C_{ds}$  Capacitance between drain and source (F)

$C_{gs}$  Capacitance between gate and source (F)

$I_{ds}$  Drain current (A)

*I<sub>F</sub>* Forward current of Schottky diode (A)

k Boltzmann's constant (eV/K)

$W_{N-}$  Width of drift region (cm)

$L_D$  Drain-to-source switching loop parasitic inductance (H)

$L_G$  Gate-to-source switching loop parasitic gate inductance (H)

$L_S$  MOSFET source-leg parasitic inductance (H)

$N_{N-}$ ,  $N_{D}$  Doping concentration of drift region (cm<sup>-3</sup>)

q Fundamental electronic charge (C)

$R_g$  Gate resistance  $(\Omega)$

$K_{pl}$  Forward conduction device constant for GaN HEMT (A/V<sup>2</sup>)

$K_{p2}$  Reverse conduction device constant for GaN HEMT (A/V<sup>2</sup>)

$R_{on,sp}$  Specific on-resistance ( $\Omega \cdot \text{cm}^2$ )

$\lambda_I$  Channel length modulation coefficient for GaN HEMT (A/V)

$V_{th1}$  Forward gate-source threshold voltage for GaN HEMT (V)

$V_{th2}$  Reverse gate-source threshold voltage for GaN HEMT (V)

T Absolute temperature (K)

$V_{bi}$  Built-in voltage in gate source junction (V)

$V_{BD}$  Breakdown voltage (V)

$PB_1$  Built-in potential for gate-drain capacitance (V)

$PB_2$  Built-in potential for drain-source capacitance (V)

$m_1$  Junction grading coefficient for gate-drain capacitance

*m*<sub>2</sub> Junction grading coefficient for drain-source capacitance

$V_{diode}$  Voltage across Schottky diode (V)

$V_{ds}$  Voltage applied to drain and source (V)

$V_{gs}$  Voltage applied to gate and source (V)

$V_{gd}$  Voltage applied to gate and drain (V)

D Ambipolar diffusion coefficient ( $cm^2/s$ )

τ High-level carrier lifetime (s)

$h_p, h_n$  Recombination parameters (cm<sup>4</sup>/s)

J Maximum current density (A/cm<sup>2</sup>)

$g_{fs}$  SiC MOSFET transconductance (A/V)

$C_L$  Load inductor equivalent parallel capacitance (F)

$C_{d1}$  SiC Schottky diode junction capacitance (F)

$L_s$  Main switching loop parasitic inductance (nH)

$L_{s2}$  Common source parasitic inductance (nH)

$Q_{gd}$  Miller charge for SiC MOSFET (C)

$R_{th(J-C)}$  Thermal resistance between junction and case (K/W)

$C_{r\theta}$  Zero-voltage-bias junction capacitance of SiC Schottky diode (F)

$T_j$  Junction temperature of power device (°C)

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 WIDE BANDGAP SEMICONDUCTOR DEVICES FOR POWER ELECTRONICS

Power electronics can be defined as the application of solid-state electronics to condition, control and convert electric power. With increasing concern for energy delivery and environmental protection, power electronics is playing an increasingly important role in human society. Power semiconductor devices are the core solid-state components in the overall power conversion system, and they most often incur the largest portion of power losses in that system. Therefore, the development of power semiconductor devices has been the driving force in the progress of power electronics systems. Until recently, silicon (Si)-based devices have dominated the power device market due to mature and well-established fabrication technology for Si. However, with the growing need for high temperature, high power density and high frequency operation, silicon devices are reaching some inherent limits in their performance. For example, a variety of applications in the aircraft, automotive, and energy exploration industries require power conversion systems to operate at an ambient temperature significantly above 200 °C, far beyond Si material limits. Consequently, a new generation of so-called wide bandgap semiconductor devices has emerged as viable replacements for the current Si-based power devices.

At present, silicon carbide (SiC) and gallium nitride (GaN) are the most promising among all wide band-gap semiconductor materials [1][2][3]. Table 1.1 compares the material properties of Si, SiC and GaN. SiC and GaN have approximately three times larger bandgap (about 3 eV) compared with Si (about 1 eV). A large bandgap results in lower leakage currents than Si, and consequently in a much higher operating temperature. The breakdown electric field of SiC and GaN is one order of magnitude higher than that of Si. The higher breakdown electric field allows the design of wide bandgap power devices with thinner and more highly-doped voltage-blocking layers. As a consequence, a lower on-state voltage drop and conduction loss for a given breakdown voltage can be achieved. The high thermal conductivity of SiC, together with the large bandgap, allows SiC-based devices to operate at temperatures easily exceeding 200 °C [4][5][6]. All of the above properties make wide bandgap semiconductor devices a promising alternative to Si-based devices.

Table 1.1 Physical characteristics of Si, SiC and GaN

| Material Property                                     | Si   | SiC | GaN  |

|-------------------------------------------------------|------|-----|------|

| Bandgap (eV)                                          | 1.1  | 3.2 | 3.4  |

| Critical Electric Field (MV/cm)                       | 0.3  | 3.2 | 3.5  |

| Electron Mobility (cm <sup>2</sup> /V·sec)            | 1450 | 700 | 2000 |

| Electron Saturation Velocity (10 <sup>6</sup> cm/sec) | 10   | 20  | 25   |

| Thermal Conductivity (W/m·K)                          | 130  | 700 | 110  |

#### 1.1.1 OVERVIEW OF COMMERCIALLY AVAILABLE SIC POWER DEVICES

A substantial amount of research and development activity has occurred over the past 20 years in the development of SiC power devices. As a result, high voltage (from 600V to 1200V) SiC unipolar power switches, such as JFETs and MOSFETs have become commercially available on the market since 2011 from Cree, Infineon and other

manufacturers [7]. Compared to conventional Si-based devices with the same voltage ratings, these SiC active power devices offer much lower on-state resistance per unit area than Si MOSFETs and much faster switching speed than Si IGBTs and GTOs. The advantages of SiC also encouraged the commercialization of SiC Schottky diodes with blocking voltages from 600 V up to 1200V by Cree, GeneSiC and other device manufacturers. These SiC Schottky diodes provide ulta-fast switching speed and almost zero reverse recovery, compared with conventional Si p-i-n diodes. Fig 1.1 shows the main SiC device manufacturers and their relevant SiC power devices (note that SemiSouth has been out of business since 2013).

Figure 1.1 Major SiC power device manufacturers and their relevant products [8]

#### 1.1.2 Overview of Commercially Available GaN Power Devices

Although GaN-based devices can theoretically offer better performance than SiC, the lack of good-quality substrates hinders the development of high-voltage vertical GaN power devices. However, the interest in GaN power devices by industry is increasing. At present, two types of GaN power devices have been reported: 1) GaN high-electron mobility transistors (HEMTs) and 2) GaN Schottky diodes. Currently, due to the lack of high quality GaN substrates, GaN epilayers are grown on substrates made of other materials, such as Si, SiC and sapphire. Silicon substrates are widely used for GaN-based devices, due to their low cost and mature fabrication techniques, even if the GaN epilayer quality is poor due to lattice mismatch. This lattice mismatch might introduce defects and lower device reliability. However, GaN substrates are becoming available, and they are expected to improve the resulting material quality and device performance.

Fig 1.2 shows the typical GaN HEMT lateral structure with three terminal contacts (source, gate and drain). A thick undoped GaN layer is grown on the Si substrate. On the top of the undoped GaN layer, an aluminum GaN (AlGaN) layer is grown. The conductivity of GaN HEMT is based on its piezoelectric property. A 2-D electron gas (2-DEG) is generated at the interface between AlGaN and GaN, with very high electron mobility (1200-2000cm<sup>2</sup>/V s) and high conductivity [9].

Several GaN HEMT products having blocking voltages ranging from 30V to 650V have been released by various manufacturers, such as EPC, GaN Systems and Transphorm. The first commercially available discrete GaN HEMTs are from Efficient Power Conversion (EPC), and they are enhancement-mode devices. The enhancement-

mode GaN device is in the off state for zero  $V_{gs}$  applied voltage, while a positive  $V_{gs}$  is needed to turn it on. Presently, enhancement-mode GaN HEMTs from EPC have blocking voltages ranging from 30V to 450V. GaN Systems offers 100V and 650V enhancement-mode GaN HEMTs. Transphorm produces depletion-mode GaN transistors with 600V rating. A depletion-mode device is naturally conductive if no voltage is applied between gate and source. To turn off the device, a negative gate-source voltage is applied so that the 2-DEG under the gate is depleted. The cascode structure shown in Fig 1.3 is used with a depletion-mode GaN device to make the whole device operate like a normally-off device. In the cascode structure, a low-voltage silicon MOSFET is connected in series with the depletion-mode high-voltage GaN HEMT and the HEMT gate is connected to the MOSFET source. The low-voltage Si MOSFET controls the ON/OFF status of the high-voltage GaN HEMT [11][12][13].

Figure 1.2 GaN HEMT structure [10]

Figure 1.3 Cascode structure for depletion-mode GaN HEMT

Significant efforts have been made on high-voltage GaN Schottky diodes for high-frequency high-power switching applications [14]. Due to the lack of high-conductivity GaN substrates, most of the reported GaN Schottky diodes are based on the lateral structure. To my knowledge, no commercial GaN Schottky diode is currently available on the market.

#### 1.2 RESEARCH MOTIVATIONS AND OBJECTIVES

The analysis and applications of wide bandgap power devices require a significant research effort, including the development of device models for wide bandgap power devices, and loss modeling of wide bandgap power devices. This dissertation describes contributions in three areas:

- 1. Development of wide bandgap power semiconductor device models

- 2. Development of analytical loss model for wide bandgap power devices

- Development of performance projection method and scalable loss model for SiC MOSFETs and SiC Schottky diodes

# 1.2.1 DEVELOPMENT OF WIDE BANDGAP POWER SEMICONDUCTOR DEVICE MODELS

Since power semiconductor device performance plays a key role in power electronics applications, power electronics designers need circuit-oriented device models to simulate the performance of power devices in different applications. The basic objective in device modeling is to obtain a predictive description of the current flow through the device as a function of the applied voltages and currents, environmental conditions, such as temperature and radiation, and physical characteristics, such as geometry, doping levels, and so on. In general, there is a trade-off between computational speed and model accuracy. The required accuracy and simulation time are crucial factors considered by device model designers when making this tradeoff. A very simple device model generally provides fast simulation speed, but does not provide physical insight into power device behavior and simulation accuracy is sacrificed. In contrast, a more complicated physics-based model is usually preferred for accurate simulation of device behavior, but it is very time-consuming and not very suitable for circuit simulations [15].

This dissertation focuses on the development of a simple and accurate circuitsimulator compact model for GaN HEMT, and a physics-based model for SiC MOSFET body diode.

# 1.2.2 DEVELOPMENT OF ANALYTICAL LOSS MODEL FOR WIDE BANDGAP POWER DEVICES

In power converter design, power losses of the power semiconductor devices are important because they strongly affect the efficiency of the power converter circuits and

determine the dimensioning of their cooling systems [16][17]. An accurate power loss model of the power semiconductor devices is needed for switching power converter design. Analytical loss models use closed form mathematical equations to accurately describe power loss mechanisms and quantify losses as a function of various design parameters. The efficiency and power loss can be estimated based on these analytical loss models.

In this project, my research focuses on analytical loss model development of SiC power semiconductor devices, such as SiC MOSFET and SiC Schottky diode. The proposed loss model should be able to accurately estimate the power losses, which are critical to evaluate the efficiency and physical size of power converters.

1.2.3 DEVELOPMENT OF PERFORMANCE PROJECTION METHOD AND SCALABLE LOSS MODEL FOR SIC MOSFETS AND SIC SCHOTTKY DIODES

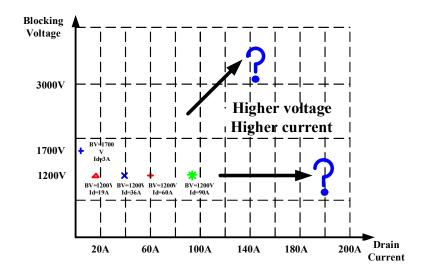

In 2011, Cree launched industry's first commercial SiC power MOSFET, which provided blocking voltage up to 1200V with an 80mΩ on-resistance at room temperature. Cree and other semiconductor manufacturers are also evaluating SiC power MOSFETs with higher blocking voltages (>1.2kV). However, higher-voltage SiC MOSFETs (>1.7kV) are not commercially available at the present time. Consequently no datasheet data is available and only limited sample device characterization has been published in the literature. In order to analyze the device behavior of upcoming high-voltage SiC MOSFETs (>1.7kV), power electronics researchers and engineers have a need for methods for future device performance projection.

The Schottky diode is also a very attractive unipolar device, formed by an electrically non-linear contact between a metal and a semiconductor bulk region. Cree has recently introduced its SiC Schottky diode products, with rated voltage ranging from 600V to 1700V, and rated current ranging from 1A to 100A. SiC Schottky diode is a very promising candidate to replace in the future silicon p-i-n diode for blocking voltage range from 600V to 3000V. Performance projection of SiC Schottky diodes for higher voltage and higher current ratings are also of interest for power electronics engineers.

Therefore, performance projection method and scalable loss model for SiC power devices are needed in system-level simulators like Smart Ship Systems Design (S3D) for power electronics researchers. S3D is a ship design tool that is capable of performing electric ship design concept development. It is critical to be able to project future SiC converter performance as the wide bandgap device technology advances. The objective of the proposed research is to produce models that accurately predict future SiC device performance. The proposed model will be able to answer system level questions such as converter efficiency, power dissipation, thermal cooling requirements and semiconductor temperature estimation.

#### 1.3 STATE OF THE ART IN RESEARCH

#### 1.3.1 GAN HEMT MODELS

Power GaN devices have evolved rapidly in recent times. In particular, the GaN high-electron-mobility transistor (HEMT) is the most promising active device in GaN. GaN HEMT has a better Baliga figure of merit compared to state-of-the-art Si MOSFETs, because GaN HEMT has the features of low on-state resistance, small

parasitic device capacitance and high critical electric field [18]. As a result, GaN HEMT can switch at faster speeds and exhibit lower power loss. So far several device models have been proposed for GaN HEMT, most of them based on device physics. These physics-based device models provide more accuracy but have some disadvantages: they typically require several device parameters (which are usually unavailable to circuit designers) to apply the model to a specific device, they are complicated and require long simulation time [19]. Additionally, most of these models have originally been developed for RF or microwave applications, which are quite different from power electronics applications. Very few papers have been published on the development of device model for GaN HEMT in the power conversion area. In [20], a simple GaN power transistor model for DC-DC converters has been proposed, and it is shown to have good static characteristics in most respects. However, the paper does not provide switching characteristics and does not consider the reverse channel current conduction behavior of GaN HEMT. The reverse channel current conduction is of vital importance, because the GaN transistor has no body diode. When GaN HEMT is required to operate in the third quadrant, the reverse channel current conduction from source to drain functions as an equivalent body diode. In [21], a GaN HEMT model has been developed in SaberRD and static I-V and C-V characteristics have been validated, but the validation of switching characteristics is not provided.

#### 1.3.2 SIC MOSFET BODY DIODE MODELS

In inductive hard switching, SiC MOSFET body diode is used if no external antiparallel diode is connected. For example, in a synchronous buck converter the inductor current flows through the lower MOSFET body diode in a synchronous buck converter

during the dead time periods. In [22], the feasibility of using SiC MOSFETs in synchronous rectification is investigated. SiC MOSFET body diode shows less reverse recovery than Si MOSFET body diode, due to the shorter carrier lifetime in SiC material. In order to utilize the body diode of SiC MOSFET, a complete characterization (static and dynamic) of SiC MOSFET body diode is required. In addition, a circuit-oriented device model is needed to evaluate the performance of SiC MOSFET body diode in power converter design. However, only few papers investigate the characteristics of SiC MOSFET body diode and device model development of SiC MOSFET body diode.

A comparative performance study of Si and SiC MOSFET body diodes is conducted in [23]. The static and dynamic characteristics of Si and SiC MOSFET body diode are demonstrated. However, the characterization of SiC MOSFET body diode is not completed. For example, the temperature-dependent static characteristics of SiC MOSFET body diode are not available. In [24], the authors investigate the switching characteristics of SiC MOSFET body diode at varied temperatures, and switching loss from reverse recovery. In addition, in [25] the body diode turn-off behavior is characterized under different turn-off voltages, forward currents, current commutating slopes and junction temperatures.

In [26], A Fourier series method to model SiC MOSFET body diode is introduced. This model uses the Fourier series solution to the ambipolar diffusion equation. However, this model is not validated over a wide temperature range. The parameter extraction method for this model is not shown, which is crucial to the practicality of the model for the circuit designers.

#### 1.3.3 ANALYTICAL LOSS MODEL FOR SIC POWER DEVICES

Power losses in power semiconductor devices consist of conduction loss and switching loss. The conduction loss can be accurately estimated from the device static I-V characteristics. The switching loss is dependent not only on device parameters, but also on circuit parameters, such as gate drive current, stray inductances and device parasitic capacitances. For switching loss estimation, the simplest analytical loss model treats power switch turn-on and turn-off current and voltage waveforms as piecewise linear. This conventional loss model yields closed form equations that can be easily used to calculate device switching loss. However, this model does not take into account parasitic elements from PCB layout and devices packages. Therefore, the loss prediction based on piecewise linear loss model is not accurate and does not match experimental results very well, especially for high frequency switching operation. In order to improve the accuracy of the analytical loss model, parasitic inductances in circuit and device capacitances should be considered.

Some papers have been published to propose analytical loss models for Si MOSFET. In [27] and [28], the effect of the nonlinearity characteristics of MOSFET capacitances is included in the proposed loss models. In addition, the parasitic inductances from PCB and device packages are also considered. The drawback of these models is their complexity. In [29], an analytical switching loss model is proposed for synchronous buck voltage regulators. The equations to calculate the rise and fall times are given. The impact of parasitic inductances is included in the model. However, the model is originally developed for low voltage Si MOSFETs, not for high voltage SiC MOSFETs. In addition, the MOSFET turn-off ringing loss is not included in the model.

# 1.3.4 PERFORMANCE PROJECTION METHOD AND SCALABLE MODEL FOR SIC POWER DEVICES

To my knowledge, no scalable loss model that provides performance projection capability for future SiC MOSFETs and SiC Schottky diodes can be found in the literature. A performance projection method and scalable loss model for future SiC power devices is a new research work in academia.

#### 1.4 Contributions

There are four original contributions in this dissertation.

First, a simple and accurate circuit-simulator compact model for gallium nitride (GaN) high electron mobility transistor (HEMT) is proposed and validated under both static and switching conditions [30]. A novel feature of this model is that it is valid also in the third quadrant, which is important when the device operates as a freewheeling diode. The only measurements required for the parameter extraction are simple I-V static characteristics and C-V characteristics. A parameter extraction procedure is proposed. A double-pulse test-bench is built to characterize the resistive and inductive switching behavior of the GaN device. A simulation model is built in Pspice software tool, considering the parasitic elements associated with the PCB interconnections and other components (load resistor, load inductor and current shunt monitor). The Pspice simulation results are compared with experimental results. The comparison shows good agreement between simulation and experimental results under both resistive and inductive switching conditions. Operation in the third quadrant under inductive switching is also validated.

Second, the static and dynamic characterizations of SiC MOSFET body diode are presented. To my knowledge, this is the first complete characterization of SiC MOSFET body diode in literature. The static characterization of SiC MOSFET body diode is carried out using a curve tracer. The I-V curves of SiC MOSFET body diode at varied junction temperatures are given. The dynamic characteristics of SiC MOSFET body diode are tested based on a double pulse test bench. The switching behavior of SiC MOSFET body diode at different current commutating slopes, forward conduction currents and junction temperatures is demonstrated. The body diode device model is described in detail. A parameter extraction procedure is introduced to increase the practicality of the model for the circuit designers. The parameter extraction requires only data from the manufacturer's datasheets and one simple switching measurement. The body diode model is validated by experimental results over a wide temperature range.

Third, a simple and accurate analytical loss model for SiC power devices is developed. This model takes into account device capacitances and the parasitic inductances in the circuit, which is a very important feature for circuit designers. In addition, the ringing loss and the loss from reverse capacitive charging current of SiC Schottky diode are considered. The turn-on and turn-off transitions are analyzed in detail. The accuracy of the proposed model is validated by numerous experimental results, and the accuracy comparison of the proposed loss model and piecewise linear loss model is presented.

Finally, a performance projection method and a scalable loss model for SiC MOSFETs and SiC Schottky diodes are proposed [31]. To my knowledge, this is the first scalable loss model that provides performance projection capability for future SiC

MOSFETs and SiC Schottky diodes. The parameters of these models are extracted from device datasheets by using a curve fitting method. Loss estimation of future SiC MOSFETs and SiC Schottky diodes can be performed based on the proposed scalable loss model.

#### 1.5 DISSERTATION ORGANIZATION

Based on the above objectives, the dissertation is organized as follow:

Chapter 2 presents a simple and accurate circuit-simulator compact model for GaN HEMT. The static and switching characterizations on GaN HEMT are conducted. The only measurements required for the parameter extraction are simple I-V static characteristics and C-V characteristics. A parameter extraction procedure is proposed. The model for GaN HEMT is validated by numerous experiments over a wide temperature range.

In Chapter 3, the static and dynamic characterizations of SiC MOSFET's body diode are presented. The body diode device model is described in detail. A parameter extraction procedure is introduced to increase the practicality of the model for the circuit designers. Validation with experimental results demonstrates the accuracy of the body diode model.

Chapter 4 proposes a simple and accurate analytical loss model for SiC power devices. The turn-on and turn-off transitions are analyzed. The accuracy of the proposed model is validated by numerous experimental results, and the accuracy comparison of the proposed loss model and piecewise linear loss model is presented.

Chapter 5 develops a performance projection method and a scalable loss model for SiC MOSFETs and SiC Schottky diodes. The parameters of these models are

extracted from device datasheets by using a curve fitting method. Loss estimation of future SiC MOSFETs and SiC Schottky diodes can be performed based on the proposed scalable loss model.

Chapter 6 summaries the dissertation and gives some ideas for future work.

#### CHAPTER 2

# CHARACTERIZATION AND MODELING OF A GALLIUM NITRIDE POWER HEMT

Gallium Nitride (GaN) is considered one of the most promising semiconductor material candidates for high-frequency, high-efficiency and high-power-density power conversion applications with significant advantages over silicon because of its excellent electrical properties, such as wider bandgap, higher thermal conductivity and higher critical breakdown electric field [32][33]. The GaN high-electron-mobility transistor (HEMT) is the most promising active device in GaN and is currently available from various manufacturers, such as EPC, International Rectifier, Transphorm, GaN Systems and others. GaN HEMT has a better Baliga figure of merit compared to state-of-the-art Si MOSFETs, because GaN HEMT exhibits low on-state resistance, small parasitic device capacitance and high critical electric field [34]. As a result, GaN HEMT can switch at faster speeds and exhibit lower conduction and switching losses [35][36][37]. Since power semiconductor device performance plays a key role in power electronics applications, power electronics designers need validated circuit-oriented device models to evaluate the performance of GaN HEMTs in different applications. The objective of this work is to develop a simple and accurate circuit-simulator compact device model, and validate it for commercially available GaN HEMT devices under static and switching conditions.

In this chapter, a simple and accurate circuit-simulator compact model for Gallium Nitride (GaN) high electron mobility transistor (HEMT) is proposed and validated under both static and switching conditions. A novel feature of this model is that it is valid also in the third quadrant, which is important when the device operates as a freewheeling diode. The only measurements required for the parameter extraction are simple I-V static characteristics and C-V characteristics. A detailed parameter extraction procedure is presented. Furthermore, a double-pulse test-bench is built to characterize the resistive and inductive switching behavior of the GaN device. A simulation model is built in Pspice software tool, considering the parasitic elements associated with the PCB interconnections and other components (load resistor, load inductor and current shunt monitor). The Pspice simulation results are compared with experimental results. The comparison shows good agreement between simulation and experimental results under both resistive and inductive switching conditions. Operation in the third quadrant under inductive switching is also validated.

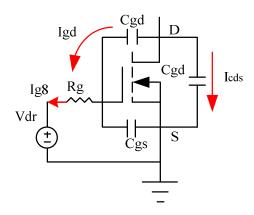

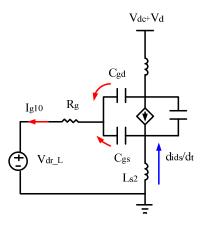

#### 2.1 DEVELOPMENT OF DEVICE SIMULATION MODEL

The simple circuit-simulator compact GaN HEMT model developed in this work is shown in Fig 2.1. The model comprises a voltage-dependent current source  $I_{ds}$ , two voltage-dependent capacitances  $C_{gd}$  and  $C_{ds}$ , a voltage-independent gate-source capacitance  $C_{gs}$ , and three parasitic resistances  $R_g$ ,  $R_s$  and  $R_d$ . The voltage-dependent current source  $I_{ds}$  is used to model static current-voltage (I-V) characteristics for both forward and reverse conduction. The three parasitic capacitances play a vital role in determining device switching performance.

## 2.1.1 Voltage-Dependent Current Source $I_{DS}$

The voltage-dependent current source  $I_{ds}$  is a bidirectional current source function of internal device node voltages  $V_{ds}$  and  $V_{gs}$ . Since the device has a nearly symmetrical lateral structure, a positive gate-to-drain voltage will enhance channel conduction in the third quadrant in the same way as a positive gate-to-source voltage does in the first quadrant. Therefore, the forward and reverse channel conduction modes are both taken into account. In order to accurately predict power converter performance at different operating temperatures, accurate temperature-dependent device constant  $K_p$  is used in the circuit model.

Figure 2.1 Structure of the GaN HEMT model

The model I-V characteristics are calculated using the following equations for the four operating modes: forward linear, forward saturation, reverse linear and reverse saturation mode.

1) Linear region in forward conduction mode (V<sub>ds</sub>>0)

Operation in this region occurs when the gate-source voltage bias  $V_{gs}$  is larger than the gate threshold voltage for forward channel conduction  $V_{th1}$ , and the internal node voltage bias  $V_{ds}$  satisfies the equation

$$V_{ds} < V_{gs} - V_{th1}$$

Equation 2-1

Under this condition, the current of the voltage-dependent current source is given by:

$$I_{ds} = K_{p1} [(V_{gs} - V_{th1})V_{ds} - V_{ds}^2 / 2]$$

Equation 2-2

where  $K_{p1}$  is the temperature-dependent device constant in forward conduction mode.

2) Saturation region in forward conduction mode (V<sub>ds</sub>>0)

When the internal node voltage bias V<sub>ds</sub> satisfies the equation

$$V_{ds} > V_{gs} - V_{th1}$$

Equation 2-3

the drain bias causes the device channel to pinch off at the drain end and the current is given by:

$$I_{ds} = K_{p1}(V_{gs} - V_{th1})^2 (1 + \lambda_1 V_{ds}) / 2$$

Equation 2-4

where  $\lambda_l$  is the channel length modulation parameter for forward channel conduction.

3) Linear region in reverse conduction mode (V<sub>ds</sub><0)

Whereas for forward conduction  $(V_{ds}>0)$  the voltage that controls channel conduction is the gate-source voltage  $V_{gs}$ , for reverse conduction  $(V_{ds}<0)$  the drain and source terminals reverse their roles and the controlling voltage is the gate-drain voltage  $V_{gd}$ . When the gate-drain voltage bias  $V_{gd}$  is larger than the threshold voltage for reverse channel conduction  $V_{th2}$ , the channel current in this linear region is given by:

$$I_{ds} = -K_{p2}[(V_{gd} - V_{th2})V_{sd} - V_{sd}^2/2]$$

Equation 2-5

where  $K_{p2}$  is the temperature-dependent device constant in reverse conduction mode.

4) Saturation region in reverse conduction mode (V<sub>ds</sub><0)

When the voltage  $V_{sd}$  satisfies the equation

$$V_{sd} > V_{gd} - V_{th2}$$

Equation 2-6

the reverse conducting channel is pinched off at the source end and the current is given by

$$I_{ds} = -K_{p2}(V_{gd} - V_{th2})^2 / 2$$

Equation 2-7

## 5) Off region in both forward conduction and reverse conduction modes

For positive drain-source voltage, when  $V_{gs}$  is smaller than threshold voltage  $V_{th1}$ , the channel in forward conduction is off and channel current  $I_{ds}$  is equal to zero. Similarly, for negative drain-source voltage, when  $V_{gd}$  is lower than threshold voltage  $V_{th2}$ , channel current  $I_{ds}$  is also equal to zero, because the conduction channel is off in this case.

# 2.1.2 Parasitic Capacitances $C_{\text{GS}}$ , $C_{\text{GD}}$ and $C_{\text{DS}}$

Since gate-source capacitance is relatively independent of the voltage potentials applied to the electrodes, a constant gate-source capacitance  $C_{\rm gs}$  is used in this device model. This assumption is justified by device capacitance measurement shown in Fig 2.8.

Capacitances  $C_{gd}$  and  $C_{ds}$  are nonlinear voltage dependent parasitic capacitances, given by:

$$C_{gd} = \frac{C_{gd0}}{\left(1 + \frac{\left|V_{gd}\right|}{PB_1}\right)^{m_1}}$$

Equation 2-8

$$C_{ds} = \frac{C_{ds0}}{\left(1 + \frac{|V_{ds}|}{PB_2}\right)^{m_2}}$$

Equation 2-9

where  $C_{gd0}$  is the zero-bias gate-to-drain capacitance, and  $C_{ds0}$  is the zero-bias drain to source capacitance.  $PB_1$  and  $PB_2$  are the junction built-in potentials for gate-drain capacitance  $C_{gd}$  and drain-source capacitance  $C_{ds}$ , respectively. The parameters  $m_1$  and  $m_2$  are the junction grading coefficients for gate-drain capacitance  $C_{gd}$  and drain-source capacitance  $C_{ds}$ , respectively.

## 2.1.3 PARASITIC RESISTANCES $R_G$ , $R_S$ AND $R_D$

The internal gate resistance  $R_g$  is assumed to be zero, compared with the external gate resistance typically introduced to dampen transient oscillations during switching transients. Resistances  $R_d$  and  $R_s$  are assumed to be constant and represent the distributed nature of terminal contact mesh.

## 2.1.4 Temperature Dependence of Device Constant $K_P$

In order to accurately estimate the device conduction loss versus temperature, the device model should include the temperature dependence of the device constant  $K_p$ ,

which determines the voltage drop across the device as a function of current. A quadratic fit for the temperature dependence of the device constant  $K_p$  is proposed:

$$K_p = K_{p0} / (1 + T_{c1}(T - T_0) + T_{c2}(T - T_0)^2)$$

Equation 2-10

where  $K_{p0}$  is the nominal device constant at room temperature,  $T_0$  is nominal room temperature, and  $T_{c1}$  and  $T_{c2}$  are temperature coefficients.

The complete list of the needed parameters for the considered device model is shown in Table 2.1.

Table 2.1 GaN HEMT model parameters

| Forward conduction device constant at room temperature          |

|-----------------------------------------------------------------|

| Reverse conduction device constant at room temperature          |

| Forward conduction threshold voltage                            |

| Reverse conduction threshold voltage                            |

| Forward conduction channel length modulation coefficient        |

| Gate-source capacitance                                         |

| Zero-bias gate-drain capacitance                                |

| Built-in potential for gate-drain capacitance                   |

| Junction grading coefficient for gate-drain capacitance         |

| Zero-bias drain-source capacitance                              |

| Built-in potential for drain-source capacitance                 |

| Junction grading coefficient for drain-source capacitance       |

| Drain parasitic resistance                                      |

| Source parasitic resistance                                     |

| Temperature coefficients for forward conduction device constant |

|                                                                 |

| Temperature coefficients for reverse conduction device constant |

|                                                                 |

|                                                                 |

#### 2.2 STATIC CHARACTERIZATION AND PARAMETER EXTRACTION

The parameter extraction approach used in this model is based on static characterization of the semiconductor device. The device under investigation is the commercially available EPC 2001 (100V/25A) from EPC. Static I-V characteristics are measured with a Tektronix 371A curve tracer, and capacitance C-V characteristics with a Keithley 590 CV analyzer.

#### 2.2.1 STATIC CHARACTERISTICS OF GAN HEMT

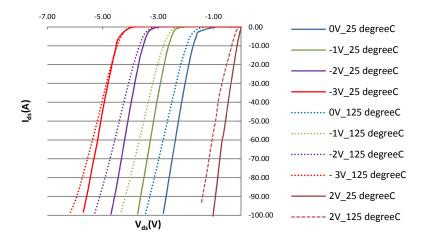

The forward output characteristic family of curves is measured under different gate-source voltage bias conditions (from 2V up to 5V) in Fig 2.2. The reverse output characteristic curves under different gate-source voltage bias conditions (from -3V up to 2V) are shown in Fig 2.3. It is interesting to notice that the reverse characteristic curves do not exhibit saturation characteristics similar to the forward characteristics curves. This is due to the fact that these characteristics are measured with a curve tracer under constant gate-source voltage  $V_{gs}$ =const, but for reverse conduction the controlling voltage is the gate-drain voltage  $V_{gd}$ . As source-drain voltage  $V_{sd}$  increases, gate-drain voltage also increases according to

$$V_{sd} = V_{ss} + V_{sd} = const + V_{sd}$$

Equation 2-11

Figure 2.2 Measured forward output I-V characteristics at room temperature 25°C for EPC2001

Figure 2.3 Measured reverse output I-V characteristics at room temperature 25°C for EPC2001

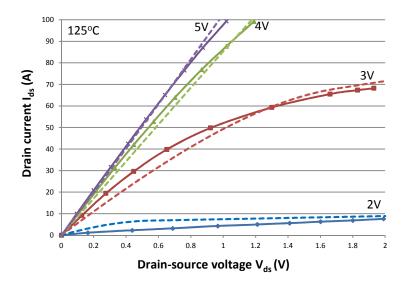

The measured forward output characteristic curves ( $V_{gs}=2/3/4/5V$ ) under operating temperatures 25°C and 125°C are shown in Fig 2.4. As seen, the slope of the I-V curve decreases with increasing temperature, indicating the decreasing channel conductivity. This is due to the lower channel carrier mobility under higher operating temperature. This device characteristic is potentially beneficial to device paralleling. Fig 2.5 shows the measured on-resistance at maximum gate-source voltage ( $V_{gs}=5V$ ) as a function of junction temperature. The measured on-resistance of GaN HEMT increases from 6.01 m $\Omega$  to 10.01 m $\Omega$ , as device junction temperature rises from 25 °C to 125 °C.

Figure 2.4 Measurement of forward output I-V characteristics at 25°C (solid) and 125 °C (dashed)

Figure 2.5 Measured on resistance of GaN HEMT at 5V gate-source voltage as a function of junction temperature

The measured reverse output characteristics curves ( $V_{gs}$ =-3/-2/-1/0/2V) under operating temperatures 25°C and 125°C show a similar behavior in Fig 2.6.

Figure 2.6 Measurement of reverse output I-V characteristics at 25°C (solid) and 125 °C (dashed)

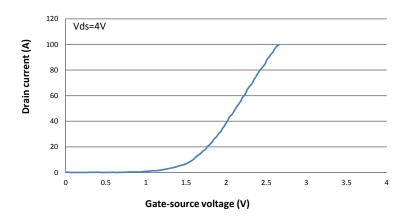

The measured transfer characteristic of GaN HEMT at room temperature is shown in Fig 2.7, which describes drain current  $I_{ds}$  as a function of gate-source voltage  $V_{gs}$  at a constant drain-source voltage  $V_{ds}$ .

Figure 2.7 Measurement of transfer characteristics at room temperature 25°C

A plot of measured device parasitic capacitances is shown in Fig 2.8. These measurements justify the choice of having a constant gate-source capacitance  $C_{\rm gs}$ , since from Fig 2.8 one can see that  $C_{\rm gs} = C_{\rm iss} - C_{\rm rss}$  is approximately constant.

Figure 2.8 Measured capacitances versus drain-to-source voltage for EPC 2001

### 2.2.2 PARAMETER EXTRACTION

The parameter extraction process for GaN HEMT is developed using only measured static I-V and C-V characteristics. The parameter extraction procedure using static characterizations is described as follows:

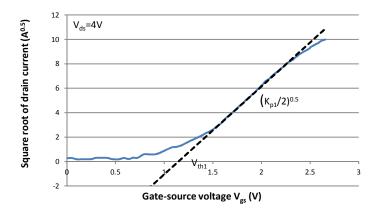

## 1) Forward conduction device constant $K_{p1}$ and threshold voltage $V_{th1}$

A curve of the square root of  $I_{ds}$  versus gate-source voltage  $V_{gs}$  shown in Fig 2.9 is plotted to extract forward conduction device constant  $K_{p1}$  and threshold voltage  $V_{th1}$ . The constant  $(K_{p1}/2)^{0.5}$  is extracted from the slope of an operating point on the curve, when the GaN HMET operates in saturation region of forward conduction. The threshold voltage  $V_{th1}$  is extracted from the point of intersection of the tangent line to the curve with the x-axis.

Figure 2.9 The plot of the square root of I<sub>ds</sub> vs. gate-source voltage

## 2) Forward conduction channel length modulation coefficient $\lambda_1$

The channel-length modulation coefficient  $\lambda_1$  is extracted from the slope of forward output I-V characteristics in the saturation region.

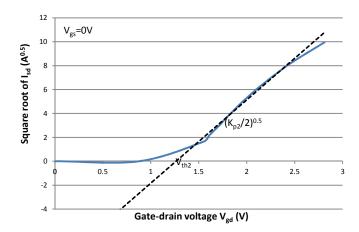

## 3) Reverse conduction device constant $K_{p2}$ and threshold voltage $V_{th2}$

A curve of the square root of  $I_{sd}$  versus gate-drain voltage  $V_{gd}$  shown in Fig 2.10 is plotted to extract reverse conduction device constant  $K_{p2}$  and threshold voltage  $V_{th2}$ . The constant  $(K_{p2}/2)^{0.5}$  is extracted from the slope of an operating point on the curve, when the GaN HEMT operates in saturation region of reverse conduction. The threshold voltage  $V_{th2}$  is extracted from the point of intersection of the tangent line to the curve.

## 4) Gate-source capacitance C<sub>gs</sub>

The gate-source capacitance  $C_{gs}$  is approximately constant. The parameter  $C_{gs}$  is extracted from  $C_{iss}$  and  $C_{rss}$  measurements.

5) Zero-bias gate-drain capacitance C<sub>gd0</sub>, built-in potential PB<sub>1</sub>, and junction grading coefficient m<sub>1</sub>:

Figure 2.10 The plot of the square root of I<sub>sd</sub> vs. gate-drain voltage

The zero-bias gate-drain capacitance  $C_{gd0}$  is extracted from  $C_{rss}$  measurement at low gate-drain bias. As shown in Fig 2.11, the junction grading coefficient  $m_1$  is extracted from the slope of gate-drain capacitance curve at high drain bias. The built-in potential  $PB_1$  is extracted from a linear interpolation of the curve. The accuracy could be improved by using a higher order interpolation at the cost of increased model complexity.

Figure 2.11 The log-log plot of C<sub>gd</sub> vs. drain-gate voltage

6) Zero-bias drain-source capacitance C<sub>ds0</sub>, built-in potential PB<sub>2</sub>, and junction grading coefficient m<sub>2</sub>:

The zero-bias gate-drain capacitance  $C_{ds0}$  is extracted from  $C_{oss}$  and  $C_{rss}$  measurements at low drain-source bias. As shown in Fig 2.12, the junction grading coefficient  $m_2$  is extracted from the slope of drain-source capacitance curve at high drain bias. The built-in potential PB<sub>2</sub> is extracted from a linear interpolation to the curve.

Figure 2.12 The log-log plot of C<sub>ds</sub> vs. drain-source voltage

## 7) Drain parasitic resistance R<sub>d</sub>, and source parasitic resistance R<sub>s</sub>